集成电路设计实践 从运放设计入门到精通

集成电路设计是现代电子工业的核心,而运放设计则是模拟集成电路中最基础、最重要的模块之一。本文将以《集成电路设计实践 运放设计 901602518.pdf》为引,探讨运放设计的核心概念与实践方法,帮助初学者快速入门。

一、运放设计的基础知识

运放(运算放大器)是一种高增益、差分输入的电压放大器,广泛应用于信号调理、滤波、模数转换等电路中。设计一个高性能的运放,需要掌握以下基础知识:

- 基本结构:包括差分输入级、增益级、输出级和偏置电路。

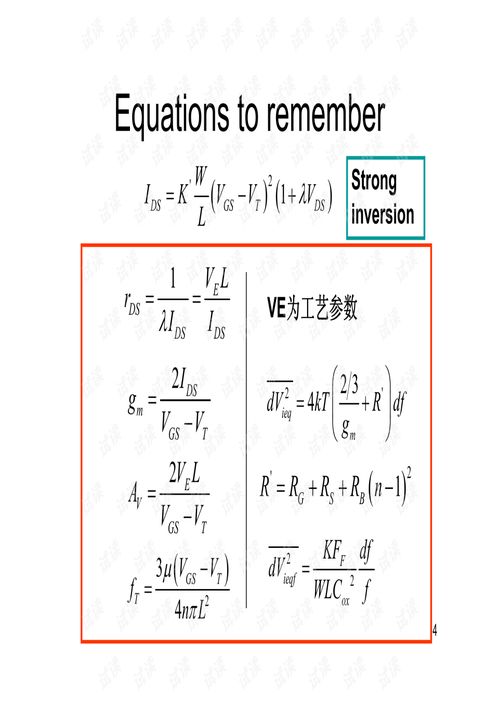

- 关键参数:如开环增益、带宽、相位裕度、共模抑制比(CMRR)、电源抑制比(PSRR)等。

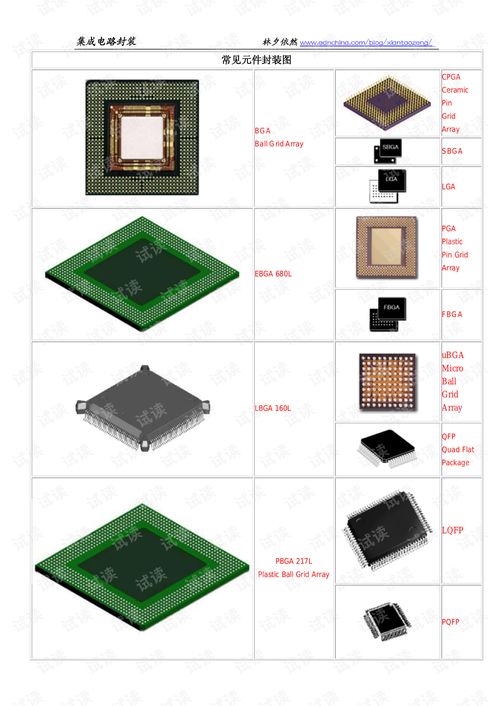

- 工艺选择:根据设计需求选择合适的CMOS或BiCMOS工艺。

二、运放设计的实践步骤

- 需求分析:明确运放的性能指标,如增益、带宽、功耗、噪声等。

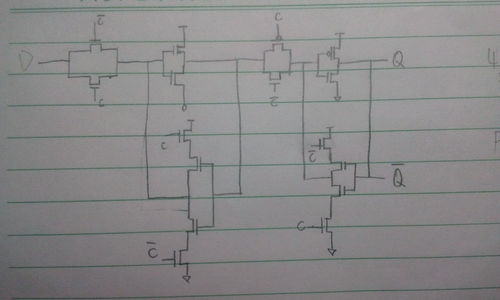

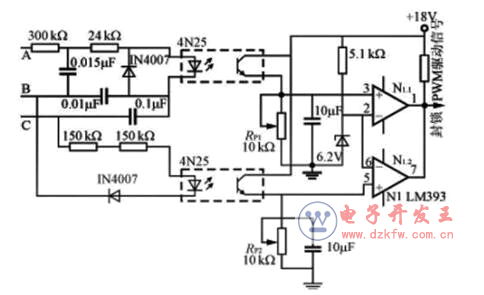

- 电路拓扑选择:根据需求选择适合的拓扑结构,如折叠共源共栅、两级运放等。

- 器件尺寸设计:通过手工计算或仿真工具确定晶体管的尺寸,确保电路满足性能要求。

- 仿真验证:使用仿真工具(如Cadence、HSPICE)进行直流、交流、瞬态和噪声仿真,优化电路性能。

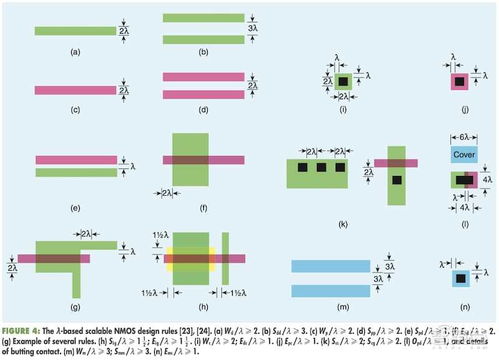

- 版图设计:绘制电路的物理版图,考虑匹配、寄生效应和可靠性问题。

- 后仿真:提取版图寄生参数后再次仿真,确保电路性能不受版图影响。

三、常见问题与解决方法

- 稳定性问题:通过米勒补偿或前馈补偿提高相位裕度,避免振荡。

- 噪声优化:增大输入对管尺寸或采用低噪声结构降低噪声。

- 功耗与性能权衡:根据应用场景调整偏置电流,平衡功耗与速度、增益的关系。

四、进阶设计技巧

对于高性能运放设计,还需关注以下方面:

- 低电压设计:在深亚微米工艺下,采用共模反馈(CMFB)或新型结构适应低电源电压。

- 高精度设计:通过校准技术或斩波调制降低失调电压和噪声。

- 系统集成:将运放嵌入更复杂的系统中,如ADC、PLL,考虑整体性能优化。

五、学习资源推荐

除了《集成电路设计实践 运放设计 901602518.pdf》外,建议参考以下资源:

- 经典教材:《模拟集成电路设计》(拉扎维著)、《CMOS模拟集成电路设计》(艾伦著)。

- 实践工具:Cadence、Synopsys等EDA工具,结合开源工具如ngspice进行仿真。

- 在线社区:EETOP等专业论坛,参与讨论并获取实际项目经验。

运放设计是集成电路设计的基石,需要理论与实践紧密结合。通过系统学习基础知识、勤于仿真实践,并不断优化设计方法,工程师可以逐步掌握高性能运放的设计能力,为更复杂的集成电路开发打下坚实基础。

如若转载,请注明出处:http://www.jabouyo.com/product/65.html

更新时间:2026-03-01 17:47:41