数字集成电路版图设计入门 从Cadence IC原理图绘制到仿真验证

数字集成电路(IC)是现代电子系统的核心,其设计流程是一个从抽象到具体、从逻辑到物理的严谨过程。其中,版图设计是连接电路设计与实际芯片制造的桥梁。本文将以业界广泛使用的Cadence设计平台为例,简要介绍数字IC版图设计的前期关键步骤:原理图绘制与电路仿真。

一、原理图绘制:设计的蓝图

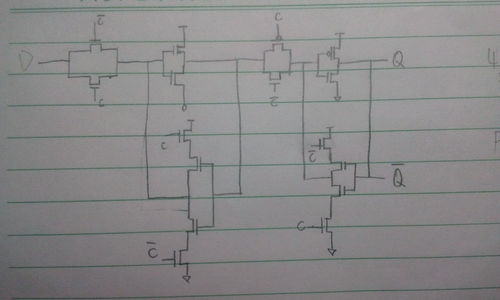

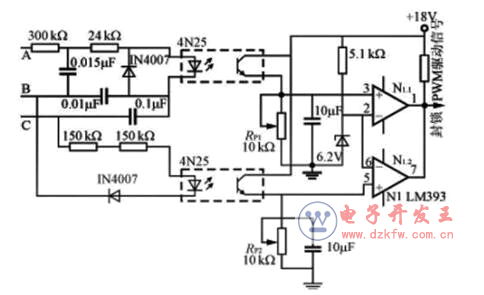

原理图绘制是数字IC设计的起点,它使用图形化的符号(如与门、或门、触发器、晶体管等)来清晰地描述电路的逻辑功能和连接关系。在Cadence IC设计环境中(如Virtuoso Schematic Editor),工程师可以:

1. 调用单元库:从标准单元库或定制库中选取所需的逻辑门或功能模块。

2. 进行连接:通过导线(Wire)将各个元器件的端口按照设计规范连接起来,形成完整的电路网络。

3. 定义属性:为电源、地、输入输出端口以及关键信号线设置电压、驱动强度等属性。

一个清晰、准确的原理图是后续所有工作的基础,它不仅体现了设计者的意图,也是团队沟通和设计审查的重要文档。

二、电路仿真:功能的验证

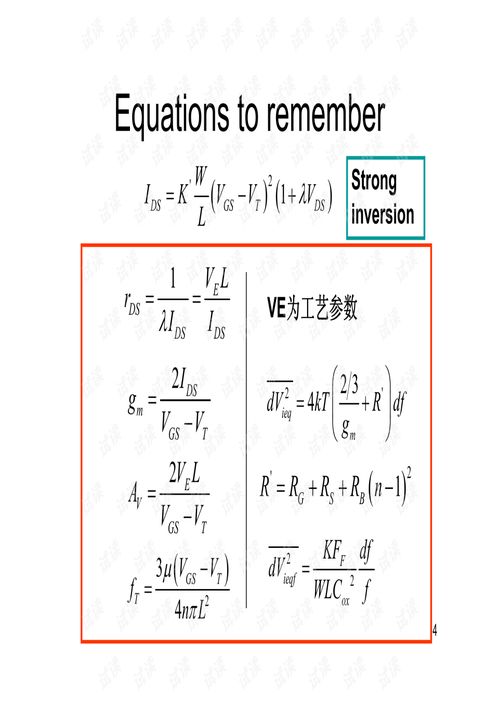

完成原理图绘制后,必须通过仿真来验证电路的功能和时序是否正确,这一步在流片(Tape-out)前至关重要。在Cadence平台中,通常使用Spectre或APS等仿真器配合ADE(Analog Design Environment)环境进行。仿真主要包含:

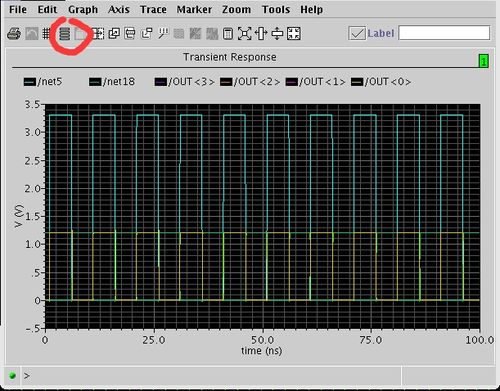

- 功能仿真:验证电路在理想情况下的逻辑行为是否与设计规格书一致。工程师需要搭建测试平台(Testbench),为电路提供各种输入激励(如时钟、数据信号),并观察输出响应。

- 时序仿真:在功能正确的基础上,引入标准单元库或晶体管模型提供的时序信息(如延迟、建立保持时间),验证电路在指定工作频率下是否能正确工作,排查是否存在时序违规(Timing Violation)。

- 仿真结果分析:利用波形查看工具(如Virtuoso Visualization & Analysis)观察信号波形,测量关键路径延迟,确保电路满足所有性能指标。

衔接与展望:从仿真到版图

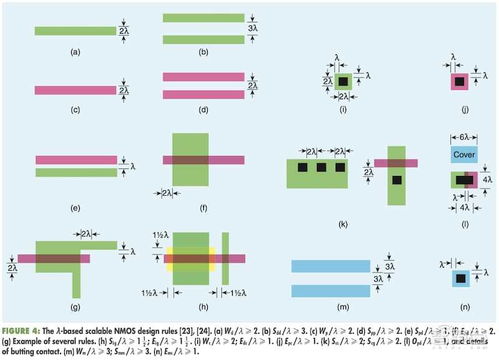

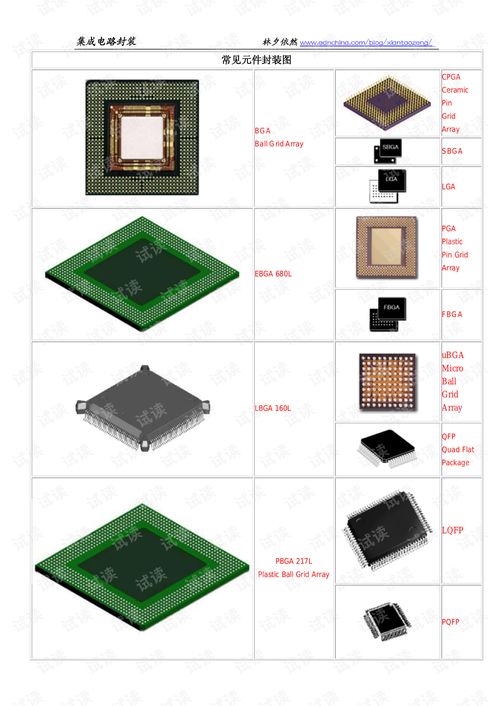

成功的原理图与仿真是后续物理版图设计的前提。只有经过充分验证的电路,才能进入版图实现阶段,即根据工艺厂的设计规则,将逻辑电路转化为由几何图形(多边形)构成的物理掩膜版图。这个过程同样在Cadence Virtuoso等工具中完成,涉及布局、布线、设计规则检查(DRC)、版图与原理图对照(LVS)等一系列复杂步骤。

掌握Cadence IC工具进行原理图绘制与仿真是数字集成电路设计工程师的基本功。它确保了设计在逻辑和时序上的正确性,为最终高性能、高可靠性的芯片实现奠定了坚实基石。

如若转载,请注明出处:http://www.jabouyo.com/product/46.html

更新时间:2026-03-01 13:19:38