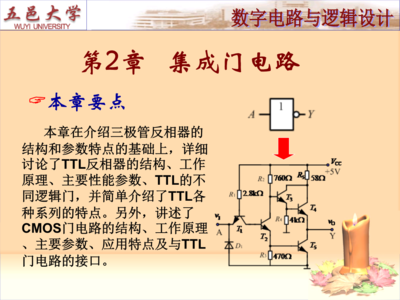

第2章 集成门电路 集成电路设计中的逻辑构建基石

集成门电路是现代数字集成电路设计的核心基础单元。它通过将基本的逻辑门(如与门、或门、非门、与非门、或非门等)以及更复杂的逻辑功能模块,高密度地制造在同一块半导体芯片上,实现了电子系统的小型化、高性能和高可靠性。

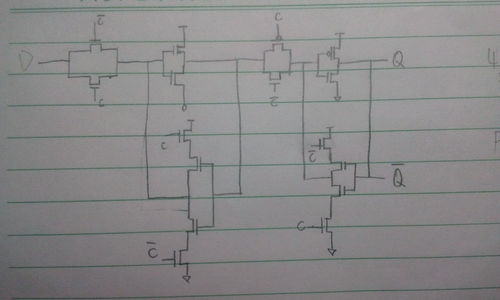

在集成电路设计中,集成门电路主要分为两大类:组合逻辑电路和时序逻辑电路。组合逻辑电路的输出仅取决于当前的输入信号组合,是构建算术逻辑单元(ALU)、编码器、译码器等模块的基础。而时序逻辑电路的输出不仅与当前输入有关,还与电路之前的状态相关,是构成寄存器、计数器、存储器及复杂状态机的核心。

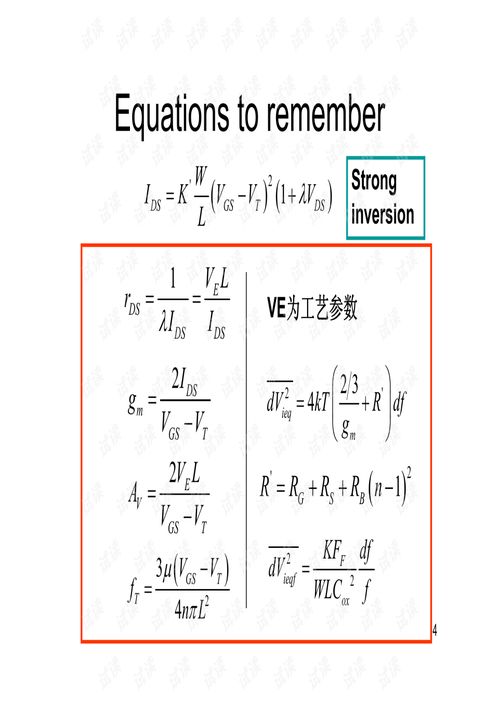

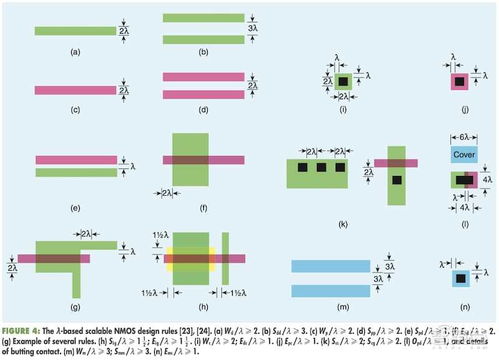

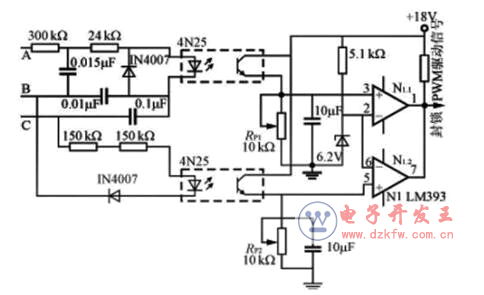

从制造工艺角度,主流的集成门电路技术包括CMOS(互补金属氧化物半导体),因其具有静态功耗低、噪声容限高、集成密度大等显著优点,已成为当今超大规模集成电路(VLSI)的绝对主导技术。设计流程通常从逻辑功能与真值表定义开始,通过逻辑化简(如使用卡诺图或EDA工具),得到优化的门级网表,再进入物理设计阶段,进行布局布线、时序验证和功耗分析。

随着工艺节点不断微缩,进入纳米尺度后,集成门电路的设计面临诸多挑战,包括功耗(特别是动态功耗和静态漏电功耗)、时序收敛、信号完整性(如串扰)、工艺变异以及可制造性设计(DFM)等问题。因此,现代设计不仅关注逻辑功能的正确实现,还必须综合考虑速度、面积、功耗之间的折衷,即所谓的“PPA”优化。

集成门电路作为集成电路的“砖瓦”,其高效、可靠的设计是构建从微处理器到片上系统(SoC)等一切复杂数字芯片的根基。掌握其设计原理、优化方法和面临的挑战,是每一位集成电路设计工程师的必备技能。

如若转载,请注明出处:http://www.jabouyo.com/product/53.html

更新时间:2026-03-01 13:12:54