集成电路封装 设计完成后的关键环节

集成电路(Integrated Circuit, IC)是现代电子技术的核心,其完整的生命周期主要包括两大关键阶段:集成电路设计和集成电路封装。设计环节决定了芯片的功能与性能,而封装环节则负责将设计好的裸片(Die)进行物理保护、电气连接、信号传输、散热管理,并最终形成一个可在实际系统中稳定工作的独立器件。本文将对集成电路封装进行概述,并阐明其与集成电路设计的紧密关系。

一、 集成电路封装的核心作用与定义

集成电路封装是指利用特定的材料(如陶瓷、塑料、金属)和工艺,将经过制造、测试合格的半导体晶圆上切割下来的独立裸片,安置在封装基板或引线框架上,并通过键合(如引线键合、倒装芯片)等方式实现裸片与外部引脚的电性连接,最后加以密封保护,形成具有标准外形尺寸和接口的成品芯片的过程。

其主要作用可归纳为以下几点:

- 物理保护:脆弱的硅裸片极易受到机械损伤、灰尘污染及潮湿、化学物质的侵蚀。封装为其提供了一个坚固的外壳,确保其在运输、安装和使用过程中的可靠性。

- 电气连接:将裸片上微米级的电路接点,通过内部互连技术(如金线、铜柱)扩展到封装外部的毫米级引脚,从而方便与印刷电路板(PCB)进行焊接和连接,构成完整的电子系统。

- 散热管理:芯片在工作时会产生热量,若热量积聚会导致性能下降甚至失效。封装结构和材料(如散热盖、导热胶)是耗散这些热量的关键路径。

- 信号完整性:随着工作频率的提高,封装内部的寄生电感和电容会严重影响信号质量。先进的封装设计致力于优化信号传输路径,减少延迟、反射和串扰。

- 标准化与小型化:封装提供了标准化的外形和引脚排列,便于系统集成。封装技术本身也在不断追求更小的体积、更高的引脚密度(如芯片级封装CSP、晶圆级封装WLP),以顺应电子产品轻薄短小的趋势。

二、 封装与设计的共生关系

集成电路封装并非一个独立于设计的后续工序,而是与芯片设计深度耦合、协同优化的过程。这种关系体现在:

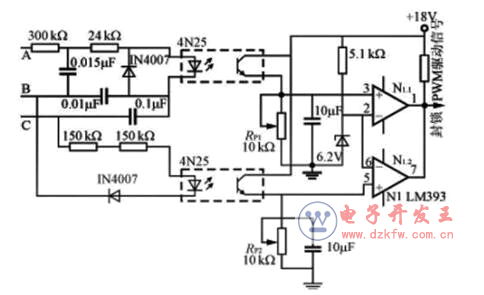

- 设计阶段的封装选型与协同设计:在芯片设计初期,就必须根据性能、成本、功耗、尺寸等目标,确定封装形式(如QFP、BGA、SiP等)。芯片的引脚定义、电源/地网络规划、高速信号线的布局,都必须与封装的引脚排布、层叠结构、布线能力相匹配。现代的高性能芯片(如CPU、GPU)普遍采用“芯片-封装协同设计”流程,通过仿真工具在早期评估封装对信号、电源完整性和热性能的影响,避免设计完成后因封装限制导致性能不达标。

- 封装技术推动设计架构演进:封装技术的进步直接扩展了芯片设计的能力边界。例如,通过2.5D/3D先进封装(如硅中介层、TSV硅通孔技术),可以将多个不同工艺、不同功能的裸片(如逻辑芯片、高带宽内存HBM)集成在一个封装体内,形成“异构集成”系统。这使得设计者能够突破单芯片在面积、功能和内存带宽上的限制,无需将所有功能都挤进单一工艺的巨型裸片中,从而实现了更优的性能、功耗和成本平衡。可以说,封装已成为实现“超越摩尔定律”的重要路径。

- 设计决定封装复杂度:芯片的晶体管数量、I/O引脚数量、工作频率和功耗水平,直接决定了所需封装的复杂程度。一个拥有数千个引脚、数百瓦功耗的高性能处理器,必然需要采用多层基板、内置热沉、精密电源网络的先进封装方案。

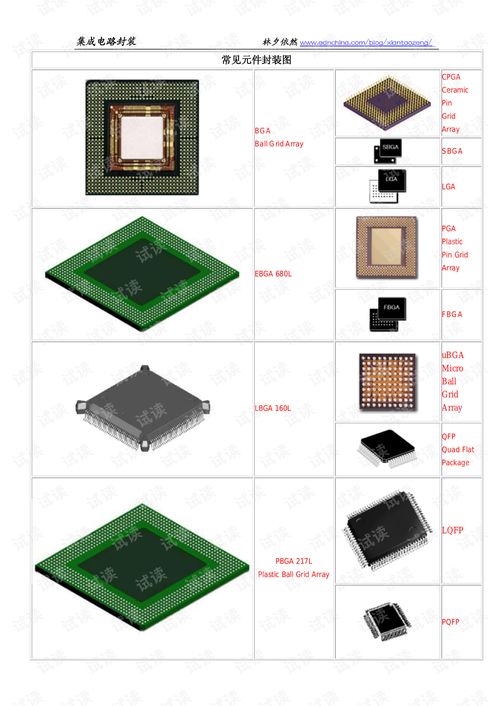

三、 主流封装技术类型简介

根据互连方式和集成度,封装技术主要沿以下路径发展:

- 通孔插装型:如双列直插封装(DIP),早期常用,现多用于简单电路。

- 表面贴装型:如四侧引脚扁平封装(QFP)、球栅阵列封装(BGA)。BGA因其更高的引脚密度和更好的电气性能,已成为主流封装形式之一。

- 芯片级封装:封装尺寸与裸片尺寸近乎相同,如晶圆级芯片尺寸封装(WLCSP),极大减小了体积。

- 系统级封装:将多个裸片和无源元件集成于同一封装内,形成一个功能完整的子系统或系统。

- 2.5D/3D集成:通过硅中介层或TSV技术,在垂直方向堆叠多个裸片,实现极高的互连密度和带宽,是当前高端计算和人工智能芯片的关键技术。

结论

集成电路封装是芯片从设计图纸走向实用产品的桥梁,是保障其性能、可靠性与可用性的关键环节。它与集成电路设计不再是简单的先后关系,而是贯穿产品开发全周期的、紧密互动的共生关系。随着半导体技术向更小节点和异构集成迈进,封装技术的创新将扮演越来越重要的角色,与芯片设计共同塑造未来电子系统的形态与能力。

如若转载,请注明出处:http://www.jabouyo.com/product/58.html

更新时间:2026-03-01 21:13:41