专用集成电路设计 打造智能时代的核心引擎

在当今信息技术飞速发展的浪潮中,集成电路(IC)作为现代电子系统的“大脑”与“心脏”,其重要性不言而喻。而专用集成电路(ASIC)设计,作为集成电路设计领域的一个重要分支,正以其高性能、低功耗和高可靠性的特点,在人工智能、5G通信、物联网、汽车电子等前沿领域扮演着至关重要的角色。

一、什么是专用集成电路(ASIC)?

专用集成电路(Application-Specific Integrated Circuit, ASIC),顾名思义,是为特定应用、特定功能或特定客户需求而专门设计、制造的集成电路。它与通用处理器(如CPU、GPU)不同,其电路结构、逻辑功能和物理版图都是针对某一特定任务进行高度优化的。这种“量身定制”的特性,使得ASIC在执行其目标任务时,往往在性能、功耗、成本和集成度上具有无可比拟的优势。

二、ASIC设计的核心流程

一个完整的ASIC设计流程是一个复杂且严谨的系统工程,通常包括以下几个关键阶段:

- 需求分析与架构定义:这是设计的起点。设计团队需要与客户或系统工程师紧密合作,明确芯片的功能、性能指标(如速度、功耗、面积)、接口协议以及目标工艺制程等。在此基础上,进行高层次架构设计,划分功能模块,确定数据流和控制流。

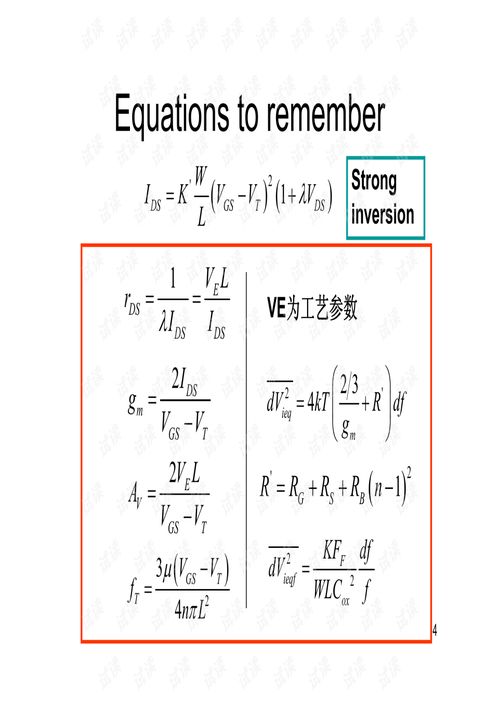

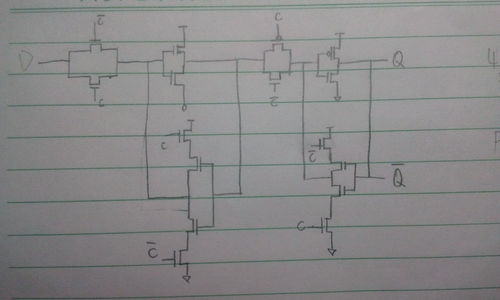

- 寄存器传输级(RTL)设计与验证:工程师使用硬件描述语言(如Verilog或VHDL)将架构转化为可综合的RTL代码。这一阶段的设计描述了数字电路在寄存器层面的数据传输与处理逻辑。与此验证工程师会构建复杂的测试平台,通过仿真等手段,确保RTL代码的功能完全符合设计规格。功能验证是保证芯片设计正确的重中之重,往往消耗整个项目过半的时间和资源。

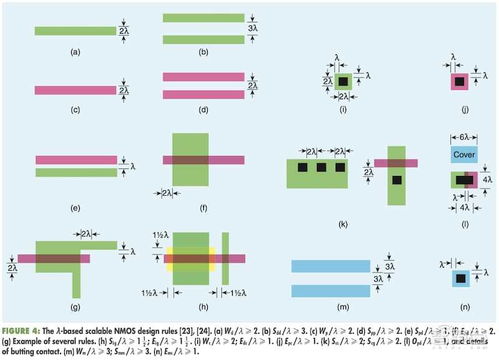

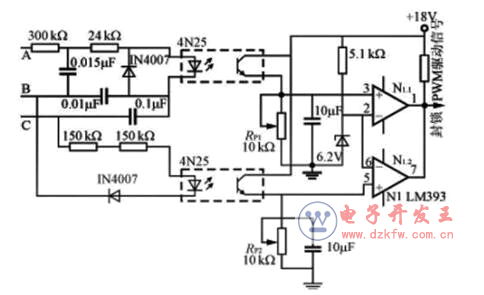

- 逻辑综合与物理设计:逻辑综合工具将RTL代码映射到目标工艺的标准单元库,生成门级网表。随后进入物理设计(后端设计)阶段,包括布局(将单元放置在芯片上)、布线(连接所有单元)、时钟树综合(确保时钟信号同步到达各个触发器)等步骤。物理设计的目标是在满足时序、功耗和面积约束的前提下,生成可用于制造的芯片版图(GDSII文件)。

- 签核与流片:在版图完成后,需要进行一系列严格的签核检查,包括时序签核(确保在最坏情况下时序仍能收敛)、功耗签核、物理验证(检查设计规则和电路连接性)等。全部通过后,将最终的GDSII文件交付给晶圆代工厂(Foundry)进行制造,这个过程称为“流片”(Tape-out)。

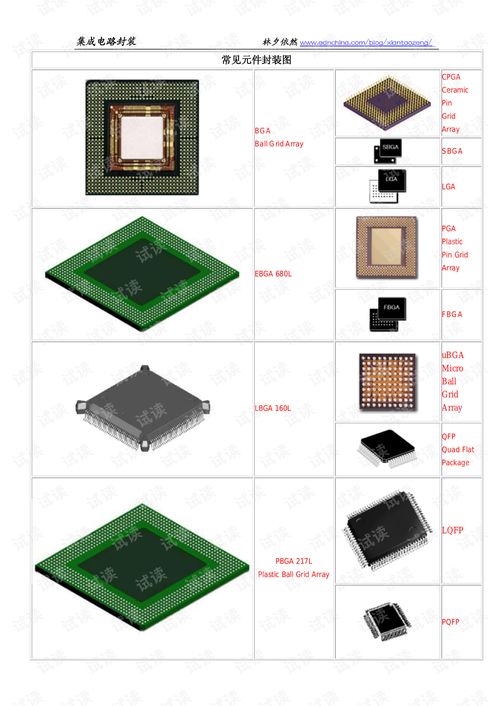

- 测试与封装:制造出的晶圆经过切割、测试,将合格的裸片进行封装,形成最终可焊接在电路板上的芯片产品。

三、ASIC设计的挑战与趋势

尽管ASIC优势显著,但其设计也面临巨大挑战:

- 高昂的成本与周期:从设计到流片,需要投入大量的人力、昂贵的EDA工具和动辄数百万美元的流片费用,且设计周期长达一至两年。

- 极高的技术门槛:涉及深亚微米/纳米级物理效应、低功耗设计、高速信号完整性、先进封装等诸多复杂技术。

- 灵活性不足:一旦流片,功能便固化,难以修改。

为了应对这些挑战,行业出现了新的趋势:

- 基于平台的ASIC和SoC:使用预先设计好并经过验证的处理器内核、总线、接口等IP模块,像搭积木一样快速构建复杂系统芯片(SoC),显著缩短设计周期。

- Chiplet与先进封装:将大芯片分解为多个功能更单一的小芯片(Chiplet),通过硅中介层、3D堆叠等先进封装技术集成,以提升良率、灵活性和性能。

- 高层次综合与敏捷开发:使用C/C++/SystemC等更高抽象级的语言进行设计,借助工具自动生成RTL代码,提升设计效率。

- 与特定领域架构融合:在AI、网络处理等领域,算法、软件、硬件协同设计,打造算法定义、软件驱动的极致能效ASIC。

四、

专用集成电路设计是连接创新想法与物理实体的桥梁,是将算法、协议和系统需求转化为硅片上精密电路的魔法。随着万物互联和智能化程度的不断加深,对计算效率、能效和可靠性的要求日益严苛,ASIC的价值将愈发凸显。它不仅是技术竞争的制高点,更是驱动智能时代持续向前的核心引擎。ASIC设计将与算法创新、先进工艺、新型材料更紧密地结合,持续拓展信息技术的边界,为人类社会创造更多可能。

如若转载,请注明出处:http://www.jabouyo.com/product/60.html

更新时间:2026-03-01 09:46:43