超大规模集成电路设计规则 通往微观世界的施工蓝图

在当今信息时代的核心,超大规模集成电路(VLSI)如同电子系统的精密大脑,驱动着从智能手机到超级计算机的一切。而构筑这些包含数十亿晶体管的微观世界的基石,正是一套严谨、详尽的设计规则。这些规则并非简单的建议,而是确保芯片功能、性能与可制造性的铁律。它们界定了物理布局的极限,是连接芯片设计理想与硅片制造现实之间的关键桥梁。

设计规则的核心理念与分类

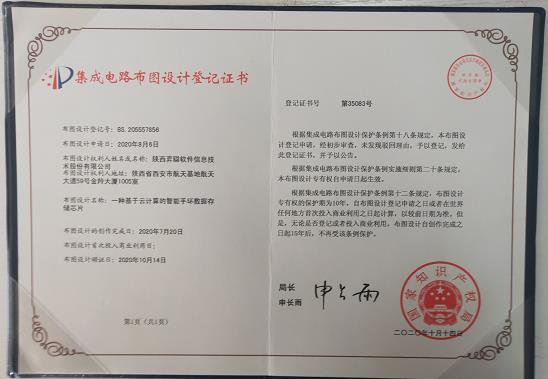

设计规则本质上是代工厂(如台积电、三星)提供给芯片设计公司(如苹果、高通)的一套几何与电气约束规范。其根本目的是在给定的半导体制造工艺下(如7纳米、5纳米),保证设计出的电路能够被高良率、可靠地生产出来。它主要解决光刻、蚀刻、离子注入等工艺步骤中固有的物理限制和偏差问题。

通常,设计规则可分为几大类:

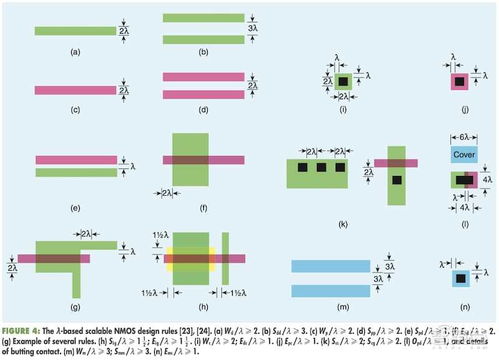

- 几何设计规则(Geometric Design Rules):这是最直观、最基础的一类,直接规定了版图中各种图形(如晶体管、金属连线、接触孔)的尺寸、间距、覆盖等几何参数。例如:

- 最小宽度:一根金属连线或一个晶体管栅极所允许的最小尺寸。这直接受到光刻分辨率极限的制约。

- 最小间距:两个相同或不同层图形之间必须保持的最小距离,以防止短路或因工艺偏差导致的桥接。

- 最小包围/延伸:要求某一层图形必须完全包围或延伸超出另一层图形一定距离。例如,接触孔必须被金属层完全包围,确保可靠的电气连接。

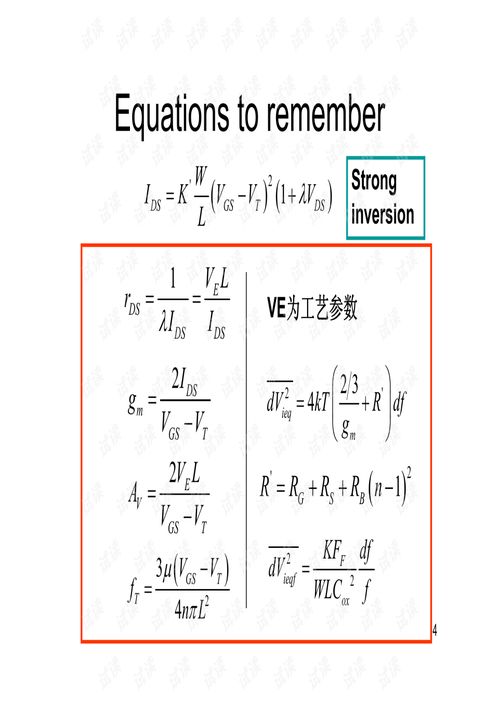

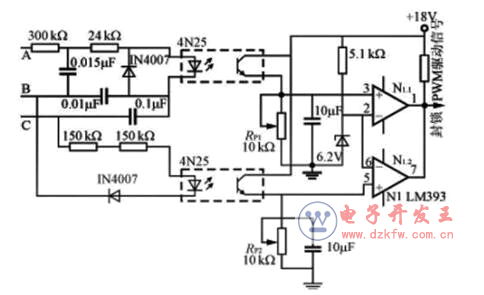

- 电气设计规则(Electrical Design Rules):这些规则与电路的性能、功耗和可靠性直接相关,通常基于几何规则和工艺的电气特性衍生而来。例如:

- 天线规则:防止在制造过程中,连接到晶体管栅极的金属连线像“天线”一样收集等离子刻蚀产生的电荷,从而击穿脆弱的栅氧层。

- 电流密度规则:规定金属连线的最大允许电流,防止因电迁移导致连线断裂或性能退化。

- 寄生参数提取规则:指导如何从版图几何结构中提取电阻、电容等寄生效应,用于精确的电路性能仿真。

实例解析:从规则到版图

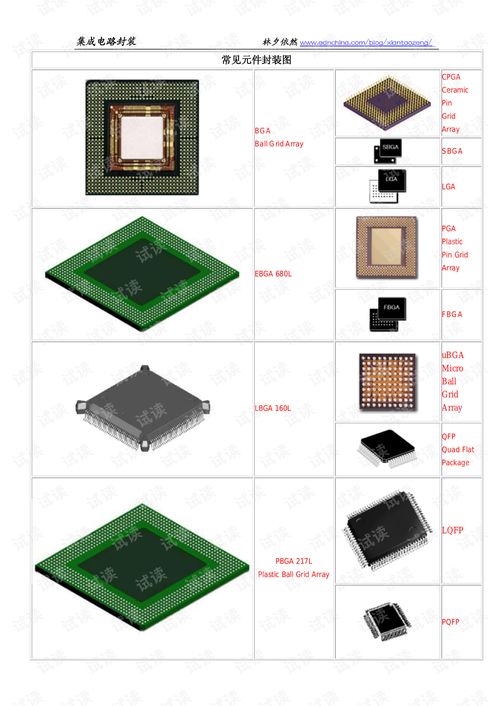

以一张典型的VLSI设计规则示意图为例(其概念源自业界通用实践),我们可以直观理解这些约束如何应用。

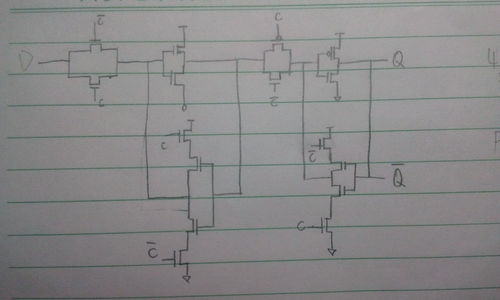

- 晶体管层级:对于构成基本开关的MOSFET,规则会严格定义有源区(晶体管沟道所在)、多晶硅栅极(控制极)以及接触孔(连接源/漏极与金属线)之间的几何关系。例如,多晶硅栅极必须与有源区充分交叠并两端延伸一定长度,以确保形成完整的沟道并容忍对位偏差。

- 互连层级:现代芯片拥有多达十余层的金属互连,像立交桥一样将晶体管连接成系统。设计规则在这里尤为关键:

- 不同层金属线之间有最小间距和最小宽度规定。

- 当金属线需要从一个层垂直连接到另一个层时,需要通过通孔。规则会规定通孔的最小尺寸、通孔与上下层金属的对齐要求、以及同一区域允许的通孔密度等。

- 对于长距离或承载大电流的电源/地线,规则可能要求使用更宽的金属线或插入大量的通孔阵列以降低电阻和满足电流密度要求。

- 密度规则:为了确保化学机械抛光(CMP)工序的均匀性,避免某些区域过度研磨或研磨不足,设计规则会要求芯片上不同区域的图形(如金属、绝缘层)保持一个全局的、均匀的密度分布。这常常需要通过添加无电气功能的“冗余图形”来满足。

挑战、演进与未来

随着工艺节点向3纳米、2纳米及以下推进,设计规则变得异常复杂和严苛。极紫外光刻(EUV)的引入、三维鳍式场效应晶体管(FinFET)乃至环栅晶体管(GAA)等新结构的应用,都带来了全新的规则类别。例如,对于FinFET,规则需要定义鳍的间距、高度以及与栅极的三维交互关系。

如今,纯粹依赖人工手动检查设计规则已不可能。电子设计自动化(EDA)工具扮演了核心角色,其设计规则检查(DRC) 功能能够自动、彻底地扫描整个版图数据库,标识出所有违反预定规则的地方,是芯片流片前不可或缺的“体检”关卡。

超大规模集成电路的设计规则是物理学、材料科学、精密制造与电子工程的结晶。它们如同一部极其精密的微观世界“建筑法典”,每一代工艺的演进都伴随着这部法典的增补与修订。正是这些看似繁琐的条条框框,约束并指引着工程师们在方寸之间,构建出改变世界的强大算力。

如若转载,请注明出处:http://www.jabouyo.com/product/64.html

更新时间:2026-03-01 23:25:48