一文看懂半导体芯片产业链 聚焦上游核心环节——集成电路设计

半导体芯片是现代电子工业的基石,其产业链复杂且高度专业化,通常被划分为上游、中游和下游三大环节。其中,上游的集成电路设计是整个产业的源头与创新引擎,决定了芯片的性能、功能与市场竞争力。

产业链全景概述

在深入探讨设计环节之前,我们首先俯瞰整个产业链的脉络:

- 上游(芯片诞生前):主要包括集成电路设计与核心IP、EDA工具及材料设备的支撑环节。这是知识和技术最密集的领域。

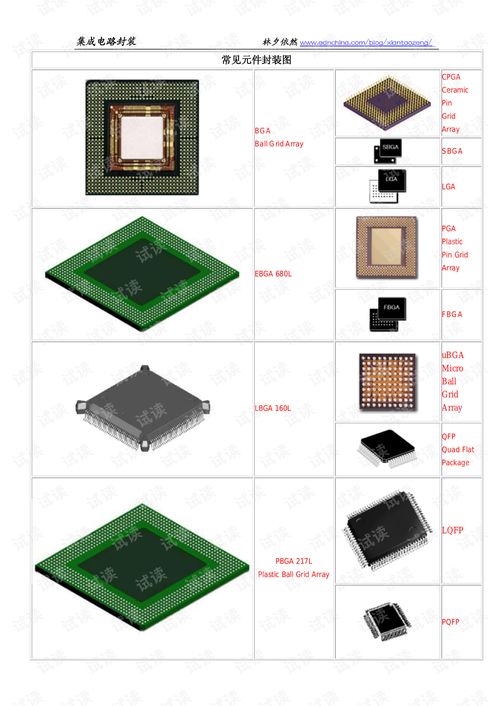

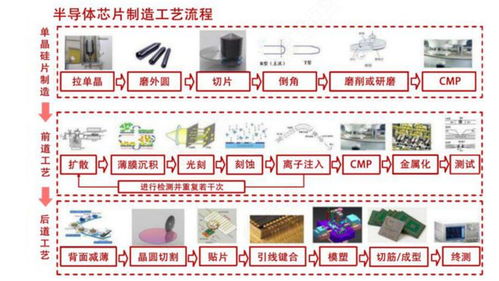

- 中游(芯片制造中):核心是晶圆制造与封装测试,即将设计好的图纸转化为实体芯片的物理实现过程,资本和技术壁垒极高。

- 下游(芯片应用端):涉及各类芯片产品(如CPU、存储器)的销售,以及将其集成到系统厂商(如手机、电脑、汽车制造商)的终端产品中,最终抵达消费者。

整个链条环环相扣,而集成电路设计作为逻辑起点,其重要性不言而喻。

核心聚焦:集成电路设计

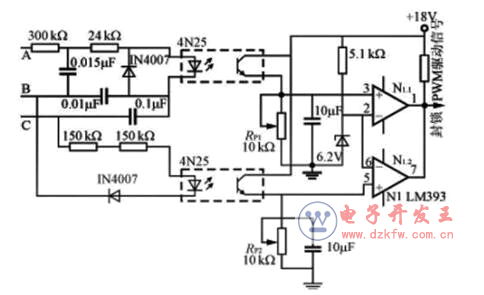

集成电路设计,常被称为IC设计或芯片设计,位于产业链最上游。其本质是根据终端应用需求,利用电子设计自动化(EDA)工具,进行逻辑与电路设计,最终输出可供制造的芯片版图(类似于建筑的“蓝图纸”)。

1. 设计流程与关键步骤

- 需求定义与规格制定:与客户或市场部门沟通,明确芯片的功能、性能、功耗、成本等目标。这是所有工作的基础。

- 架构设计:进行高层次规划,确定芯片的整体架构、模块划分以及核心算法(如CPU的流水线设计、AI芯片的神经网络加速器设计)。

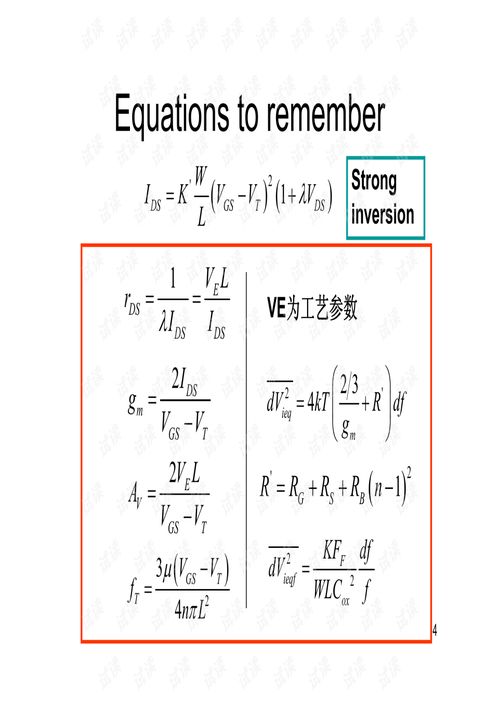

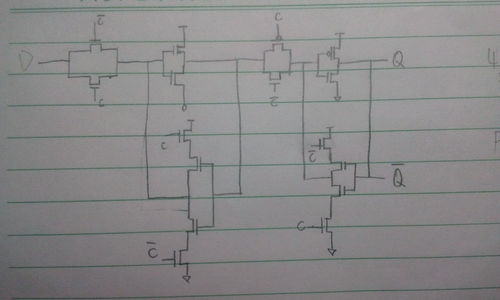

- 逻辑设计与验证:使用硬件描述语言(如Verilog、VHDL)编写代码,描述芯片各模块的逻辑功能,并通过仿真进行严格验证,确保逻辑正确。

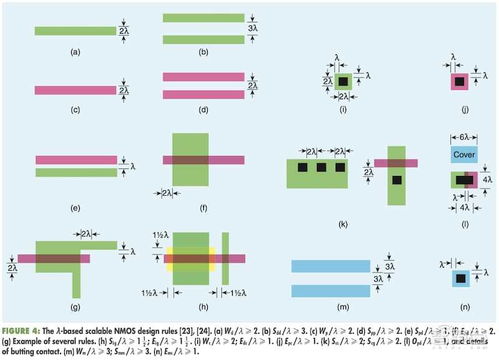

- 物理设计:将逻辑电路转化为实际的物理版图,包括布局(确定元件位置)、布线(连接所有元件)、时序与功耗分析等。这是设计与制造的桥梁。

- 交付与流片:将最终确认的版图数据(GDSII格式)交付给晶圆代工厂(Foundry),进行首次试生产,即“流片”。流片成功是设计环节完成的标志。

2. 设计模式与主要参与者

- Fabless模式(无晶圆厂设计公司):这是当今主流模式。公司只专注于芯片设计,将制造、封装测试外包给专业代工厂。例如高通(Qualcomm)、英伟达(NVIDIA)、华为海思、联发科(MediaTek)等巨头均采用此模式。它们轻资产运营,核心竞争力在于创新、设计与IP积累。

- IDM模式(垂直整合制造):公司业务覆盖设计、制造、封测全链条。如英特尔(Intel)、三星(Samsung)、德州仪器(TI)。此模式资源整合度高,但资本投入巨大。

- 设计服务与IP授权商:如ARM公司,不生产芯片,而是通过授权其处理器架构等核心知识产权(IP)给设计公司获利,是生态中的重要支撑。

3. 设计的核心支撑要素

- EDA工具:芯片设计的“画笔”和“仿真实验室”。全球市场主要由新思科技(Synopsys)、铿腾电子(Cadence)、西门子EDA(原Mentor Graphics)三大巨头垄断。没有先进的EDA工具,复杂芯片设计寸步难行。

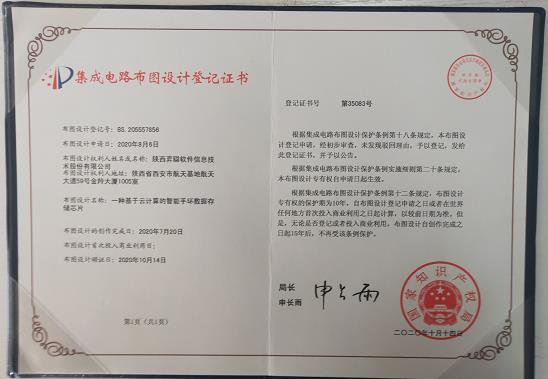

- 半导体IP核:预先设计好的、经过验证的、可重复使用的功能模块(如CPU核、接口协议IP)。使用IP核能大幅缩短设计周期,降低研发风险和成本。

- 专业人才:需要跨学科的顶尖工程师团队,精通体系结构、微电子、计算机、算法等多个领域。

设计环节的挑战与趋势

- 技术挑战:随着工艺节点向3纳米、2纳米迈进,设计复杂度呈指数级增长,功耗、散热、信号完整性等问题日益严峻。

- 高投入与高风险:先进工艺芯片设计成本动辄数亿美元,且流片失败风险巨大,对公司的资金和技术实力是终极考验。

- 未来趋势:

- 异构集成与Chiplet(芯粒):通过将不同工艺、功能的模块化芯片封装在一起,提升性能并降低成本,正在改变传统设计范式。

- 领域专用架构:针对AI、自动驾驶、数据中心等特定场景,设计专用芯片(如DPU、NPU),以获取更高的能效比。

- 全产业链协同:设计与制造(DTCO)、设计与封装(STCO)的协同优化愈发重要,要求设计公司更深入地理解中下游工艺。

###

集成电路设计是半导体产业链的“大脑”与“蓝图绘制者”,它将抽象的创意与应用需求,转化为精密复杂的物理现实。理解设计环节,是理解芯片如何诞生、以及为何高端芯片研发如此艰难的关键第一步。在全球化与科技竞争背景下,强大的芯片设计能力已成为国家科技实力的重要标志,持续驱动着下游整个电子信息产业的创新与变革。

如若转载,请注明出处:http://www.jabouyo.com/product/47.html

更新时间:2026-03-01 05:47:16