浅谈嵌入式MCU硬件设计之MCU最小系统电路与集成电路设计

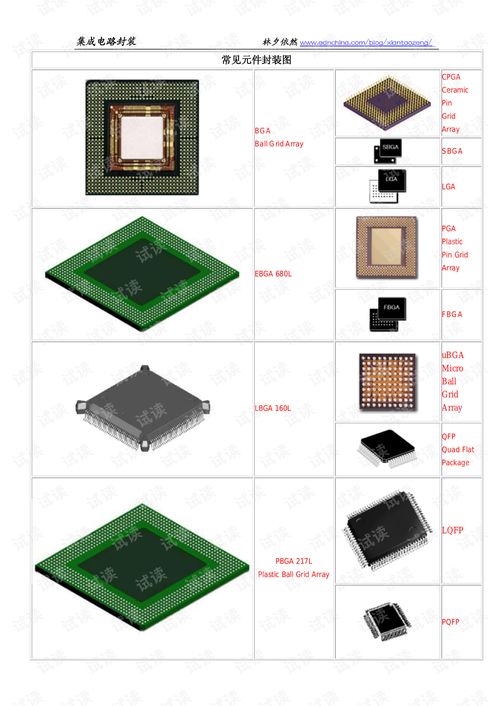

在嵌入式系统开发领域,微控制器(MCU)是核心与灵魂。一个稳定、可靠的嵌入式硬件平台始于MCU最小系统电路的正确设计。作为其物理载体的集成电路(IC)设计理念,也深刻影响着MCU的选型与应用。本文将探讨MCU最小系统电路的关键组成部分,并简述其与更宏观的集成电路设计思想之间的联系。

一、MCU最小系统电路:嵌入式硬件的基础

MCU最小系统,是指微控制器能够独立运行程序所必需的最基本外围电路。它确保了MCU在上电后能正确初始化、执行代码。一个典型的最小系统通常包含以下几个核心部分:

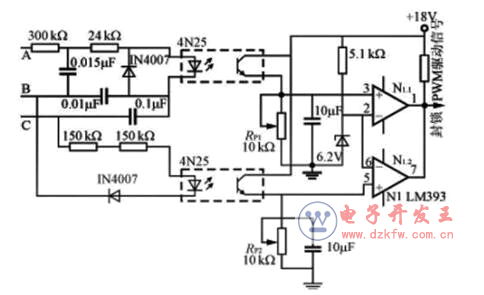

- 电源电路:为MCU提供稳定、洁净的直流工作电压。设计时需注意电压等级(如3.3V、5V)、功耗估算,并必须加入去耦电容(通常为0.1μF的陶瓷电容靠近电源引脚放置),以滤除高频噪声,确保内核及I/O电源的稳定性。

- 复位电路:确保MCU在上电或异常时能可靠地恢复到已知的初始状态。主要有上电复位(通过RC电路实现简单延时)和手动复位两种。许多现代MCU也集成了内部复位源,但外部复位电路对于提高系统在恶劣环境下的可靠性仍至关重要。

- 时钟电路:为MCU提供工作节拍。可分为外部时钟(有源晶振)和内部时钟(RC振荡器)两种方式。对于需要高精度定时、通信(如USB、UART)的应用,外部晶振搭配负载电容构成的谐振电路是标准选择,其布局布线需远离噪声源且路径尽量短。内部时钟则节省成本与空间,适用于时序要求不严的场合。

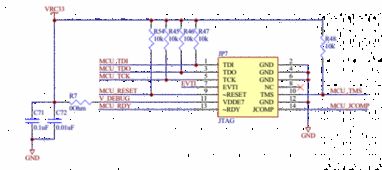

- 启动配置电路:通过设置特定的引脚电平(如BOOT0, BOOT1),决定MCU从上电后从何处开始执行代码(如系统存储器、内置Flash或SRAM)。正确的配置是程序能否加载运行的前提。

- 调试/下载接口:如JTAG、SWD等,用于程序烧录与在线调试。这是开发阶段必不可少的桥梁,设计时需注意接口信号线的上拉/下拉电阻配置及走线。

二、最小系统设计中的集成电路设计思想

MCU本身就是一个高度集成的片上系统(SoC)。其内部集成了CPU内核、存储器、定时器、多种外设接口等。因此,在规划最小系统时,实质上是在进行一次“系统级”的集成电路应用设计:

- 选型与资源评估:如同IC设计中的规格定义,需根据应用需求(性能、功耗、外设、成本)选择合适的MCU型号,评估其内部资源(Flash、RAM、GPIO数量等)是否满足要求,这直接决定了后续电路和软件的复杂度。

- 引脚复用与功能分配:现代MCU引脚普遍具有复用功能。硬件设计时需仔细查阅数据手册,合理分配引脚功能(如GPIO、ADC、通信接口),避免冲突,并考虑未使用引脚的处理方式(如上拉/下拉或配置为输出),以优化功耗与抗干扰性。

- 信号完整性考虑:尽管是板级设计,但高速信号(如外部存储器总线、高频时钟)的走线需要遵循基本的IC互连设计原则,如阻抗匹配、减少过孔、避免锐角走线,以保障信号质量。

- 电源完整性管理:MCU内部不同模块(模拟、数字、I/O)通常需要独立的电源域或滤波。最小系统设计中的电源网络布局(如使用星型拓扑、大面积铺地)直接反映了对芯片内部供电网络稳定性的支持。

- ESD与可靠性设计:在接口电路上增加ESD保护器件、TVS管等,是对MCU内部脆弱CMOS电路的必要保护,体现了从芯片到系统的可靠性延伸设计。

三、

MCU最小系统电路设计,是嵌入式硬件工程师将一颗高度集成的硅片转化为一个可控、可用的智能节点的第一步。它既是严谨的电子工程实践,也处处渗透着集成电路设计的系统思维——从芯片内部结构的理解,到外部资源的合理配置与优化。一个优秀的最小系统设计,不仅追求“能工作”,更追求在稳定性、抗干扰、可生产性及成本上的平衡,为整个嵌入式产品的成功奠定坚实的硬件基石。随着MCU集成度越来越高(集成DC-DC、射频、安全模块等),最小系统的外围电路可能会简化,但对设计者理解芯片内部架构、数据手册以及系统级设计能力的要求却愈发提高。

如若转载,请注明出处:http://www.jabouyo.com/product/51.html

更新时间:2026-03-01 11:54:34