精密的处理器 集成电路设计中的艺术与科学

在当今数字时代的核心,处理器以其令人惊叹的精密性驱动着从智能手机到超级计算机的每一台智能设备。这种精密性并非偶然,而是集成电路设计这门融合了艺术与科学的尖端学科所成就的杰作。

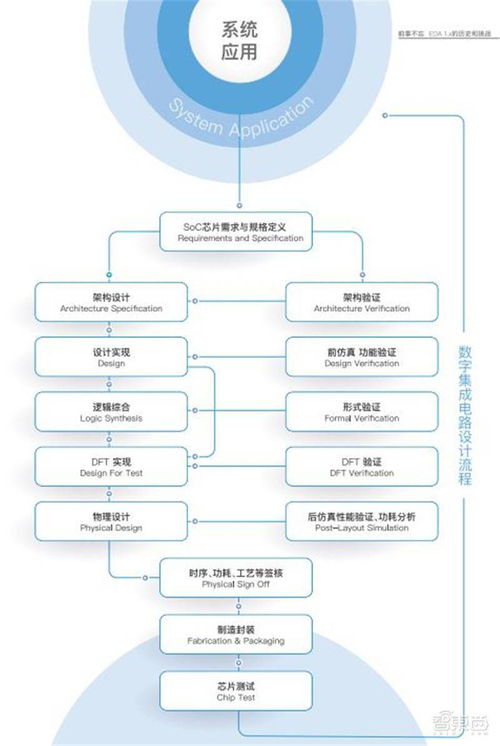

一、 设计的起点:架构与指令集

处理器的精密之旅始于顶层设计。架构师们需要做出根本性决策:是采用精简指令集(RISC)还是复杂指令集(CISC)?如何设计核心微架构以实现性能、功耗和芯片面积的完美平衡?现代处理器,如多核、众核架构,甚至引入了异构计算单元(如CPU+GPU+NPU),其设计复杂度呈指数级增长。指令集架构(ISA)作为硬件与软件之间的契约,定义了处理器的“语言”,其设计的优雅与高效直接决定了后续所有设计环节的上限。

二、 逻辑实现:从抽象到电路

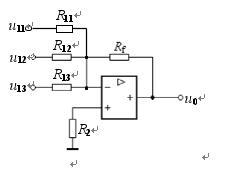

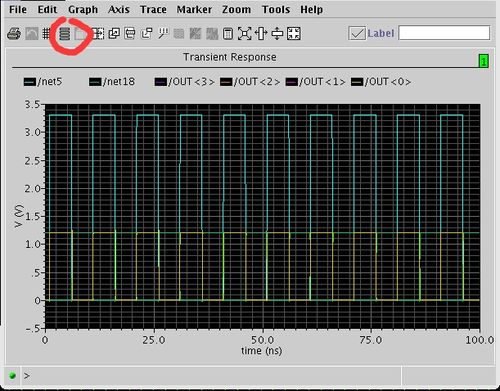

一旦架构确定,设计便进入逻辑实现阶段。工程师们使用硬件描述语言(如Verilog或VHDL),将处理器的功能(如加法器、缓存控制器、分支预测器)描述为寄存器传输级(RTL)代码。这一过程如同用代码“雕刻”出处理器的灵魂。通过逻辑综合工具,这些RTL描述被自动转化为由基本逻辑门(如与门、或门、非门)组成的网表。此时,设计从抽象的行为描述,迈向了具体的电路结构。

三、 物理设计:在纳米尺度上布局布线

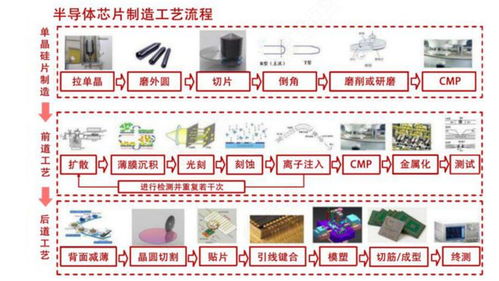

这是精密性体现得最为淋漓尽致的阶段。物理设计的目标是将逻辑网表转化为可用于制造的几何图形(版图)。

- 布局:数十亿个晶体管需要被合理地放置在芯片的二维平面上。关键路径上的元件必须靠近以降低延迟,而发热单元则需要分散以避免局部过热。这如同在微观世界里规划一座超级大都市,既要保证“交通”(信号)流畅,又要确保“居民”(晶体管)安居。

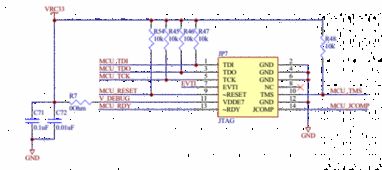

- 布线:在晶体管之间铺设连接它们的金属导线。在纳米工艺下,导线本身的电阻和电容成为影响信号速度与功耗的主要因素。设计者必须进行精密的时序分析、信号完整性分析和功耗分析,反复迭代,确保每一条信号都能在要求的时间内、以足够的强度到达目的地,且避免串扰和噪声。

- 设计规则检查:必须严格遵守晶圆厂提供的数百条物理设计规则,确保版图能够被成功制造。任何微小的违规都可能导致芯片失效。

四、 验证与仿真:确保万无一失

在投入数十亿美元进行流片制造之前,验证是确保设计正确的最后、也是最重要的关卡。工程师们构建庞大的测试平台,运行数百万甚至数十亿个测试向量,模拟处理器在各种极端和正常情况下的行为。形式验证工具则从数学上证明设计的某些属性绝对正确。随着芯片复杂度提升,验证工作所占用的时间和资源往往超过设计本身。

五、 先进技术与未来挑战

现代处理器设计正不断逼近物理极限:

- 先进工艺:从7纳米、5纳米到3纳米乃至更小,晶体管尺寸的微缩带来了性能提升和功耗降低,但也使得漏电、工艺变异和制造复杂性剧增。

- 新器件与新材料:为了延续摩尔定律,业界正在探索环栅晶体管(GAA)、碳纳米管、二维材料等全新路径。

- 系统级协同设计:处理器不再是孤立的芯片,而是与封装技术(如2.5D/3D集成)、内存(如HBM)、高速接口等紧密结合。芯片级(Chiplet)设计通过将大芯片分解为多个小芯片集成,成为提升良率和设计灵活性的关键。

- 专用领域架构:为人工智能、图形处理、网络处理等特定任务设计高度定制化的处理器核心,以达成极致的能效比,这正成为创新的热点。

精密的处理器是现代人类智慧的结晶。集成电路设计是一个不断在性能、功耗、面积、成本和开发时间之间进行精妙权衡的旅程。它既需要严谨的数学、物理和工程学基础,也需要创造性的思维来解决前所未有的挑战。随着我们步入万物智能互联的时代,对更强大、更高效、更智能的处理器的需求永无止境,而这门精密的艺术与科学,也必将继续推动着人类技术前沿的不断突破。

如若转载,请注明出处:http://www.jabouyo.com/product/35.html

更新时间:2026-03-01 20:48:34